### AKADEMIE DER WISSENSCHAFTEN DER DDR

- Zentralinstitut für Kybernetik und Informationsprozesse -

## 12. Arbeitstagung

# Entwurf von Schaltsystemen, Systementwurf

Dresden, 5. - 7. April 1983

Kurzfassungen der Vorträge

Berlin, April 1983

Zech, K.-A. (Berlin) Ein systolisches Automatenfeld zur Layout-Entwurfsregelprüfung

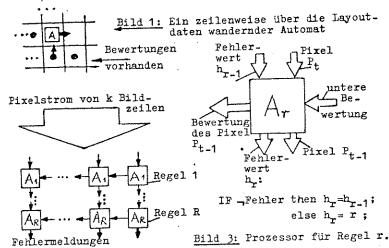

Eustace und Mukhopadhyay veröffentlichten einen automatentheoretischen Ansatz zur geometrischen Überprüfung gerasterter Layoutdaten. Hierbei wird jedem Bildpunkt, der durch einen Bitvektor (Pixel) seine Zugehörigkeit zu einer Figur in jeder Maskenebene markiert, durch Auswertung (a) der bereits ermittelten Bewertung des "linken" Bildpunktnachbarn, (b) der ebenfalls schon festgelegten Bewertung des "unteren" Nachbarbildpunktes und (c) des Pixels selbst dessen Bewertung zugeordnet. Diese Bewertung enthält einerseits verdichtet relevante Information über den links-unten liegenden Bildteil, andererseits auch eine Aussage über sich eventuell an diesem Bildpunkt auswirkende Regelverletzungen. Die Erzeugung der Bewertungen aller Bildpunkte eines Bildes kann ein Automat erledigen, der zeilenweise "von links nach rechts" über das Bild zieht, die "linken" Bewertungen als innere Zustände annimmt und dessen Eingabe aus den Pixels sowie den "unteren" Bewertungen besteht und der ggf. Fehlermarkierungen für den Punkt ausgibt, auf dem er gerade sitzt (Bild 1). Ein solcher Automat ist in der Lage, eine (komplexe) Regel zu überprüfen. Die Bestimmung der Automatenfunktionen ist etwas mühsam /1/, jedoch wesentliches Element der Flexibilität dieses Verfahrens.

Der beschriebene Ansatz wurde softwaremäßig realisiert /1/, wobei die Bestimmung des Polge\_zustandes und der Fehlermarkierung 46% der CPU-Zeit ausmachte, so daß für diese Aufgabe von den Autoren eine unterstützende Hardware (PLA oder dgl.) empfohlen wurde. Die Regularität dieser Lösung legt jedoch eine systolische /2/ Hardwarelösung (zellulares Automatenfeld, unidirektionaler Datenfluß) nahe, die nachfolgend beschrieben wird.

Für jede der betrachteten Regeln r, r=1...R, wird eine lineare Anordnung von k identischen Automaten Ar verwendet. Diese R Ketten werden gemäß Bild 2 zu einem zweidimensionalen Feld verknüpft. Dabei erfüllt jeder Automat die An-

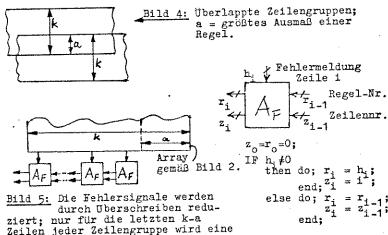

schlußbedingungen von Bild 3. Ist a die größte Ausdehnung, die eine Regel annimmt, so wird das Rasterbild zerlegt in Zeilengruppen zu je k Zeilen, die sich mit jeweils a Zeilen überlappen (Bild 4). Eine zusätzliche Kette von k-a Automaten A<sub>F</sub> zur Fehlerbehandlung gemäß Bild 5 gibt die Fehlermeldungen an ein Fehlerdisplay weiter. Durch die überlappung werden die unteren Bildbewertungen für die erste der k-a letzten Zeilen jeder Zeilengruppe reproduziert, so daß man diese nicht speichern muß. Dies hebt jede Beschränkung für die Zeilenlänge und damit die Bildgröße auf.

#### Aufwands- und Leistungseinschätzung

Die beschriebene Architektur kann etwa mittels FPLAs oder aber als Kundenwunsch-VLSIC realisiert werden. Bei unterstellter VLSI-Realisierung der Ar durch PLA-Automaten /2/, /7,8/ für 12 Regelr /1/, 5 Layoutebenen /2/, maximal 5 Zustandsbits für die Bewertungen, 4 Bitleitungen für die Fehler und (bei nicht allzu komplizierten Regeln) ca. 100 PLA-Termen erhält nan eine Fläche von rund 1800  $\lambda$  (Höhe) mal 200  $\lambda$  (Breite) für eine PLA mit dynamischen E/A-Registern, was bei dem Rastermaß  $\lambda$  = 2,5/um (/8/ 1979) 500/um mal 4500/um bedeutet.

Können die Bilddaten genügend schnell bereitgestellt werden /5/, so ergibt sich folgende Zeitabschätzung:

Bei 33 MHz Taktfrequenz kann bei k=20 und a=6 /3/ für ein Gesamtchip von 7,6 x 7,6 mm² mit  $\lambda$  = 2,5/um eine Zeit von 0,22 s angenommen werden. Diese Zahl erhöht sich auf 1,5 s für  $\lambda$  = 1/um. Hierbei muß noch eine Zeitverzögerung für die (externen) Zuleitungen einkalkuliert werden.

#### Einordnung und Zusammenfassung

Eine vorwiegend hardwaregestützte Entwurfsregelprüfung wurde in /5/ und /6/ vorgestellt. /5/ basiert auf einer Hardwarerealisierung von modifizierten Algorithmen, die den Programmen aus /5,4/ zugrundeliegen, während /6/ einen zellularen Bildverarbeitungscomputer hierfür einsetzt und

8,3

auf bildalgebraischen Betrachtungen beruht. Beide gehen von dem Baker'schen Ansatz /3/ aus, ein Fenster von maximal 4 \( \lambda \) zeilenweise über die Layoutdaten zu schieben, um den Inhalt auf Gültigkeit hin zu untersuchen. Seiler /5/ gibt für oben unterstellte Größen und \( \lambda = 1 \) um eine Bearbeitungszeit von 87 s an. Die hier angegenene systolische Struktur ist also um eine bis zwei Größenordnungen schneller und läßt sie somit als besonders attraktiv für einen interaktiven Entwurfsplatz erscheinen. Darüberhinaus ist der Eustace-Mukhopadhyay-Ansatz einfacher und flexibler, und er ist nicht auf eine bestimmte Technologie beschränkt. Er zeigt aber sein Vermögen besonders bei vereinfachten \( \lambda \)-Regeln wie die Mead/Conway-Regeln /2/ für einen einfachen nSGT-Prozeß.

#### Literatur

- /1/ Eustace, R.A.; Mukhopadhyay, A.: A deterministic finite automaton approach to design rule checking for VLSI. Proc. 19th.Design Automation Conference 1982, Las Vegas, Hevada, USA, June 14-16, 1982

- /2/ Mead, C.: Conway, L.: Introduction to VLSI Systems.

Addison Wesley, Reading, Mass., USA, 1980

- /3/ Baker, C.M.: Artwork Analysis Tools for VLSI Circuits.

MS Thesis, MIT Cambridge, Mass., USA, May 1980

- /4/ Kopec, G.E.: LSIAA: LSI Artwork Analysis System.

MIT Cambridge, Mss., USA, 1980

- /5/ Seiler, L.: A hardware assisted design rule check architecture. wie /1/

- /6/ Kudge,T.H.; Rutenbar, R.A.; Lougheed, R.M.; Atkins,D.E.:

Cellular image processing techniques for VLSI

circuit layout validation and routing. wie /1/

- /7/ Eckhardt, D., Konrad, E.; Leupold, W.: Entwurf komplexer digitaler Schaltungen. Reihe Automatisierungstechnik 175, Verlag Technik Berlin 1976

- /3/ Hon, R.W.; Sequin, C.H.: A Guide to LSI Implementation. 2nd edition, XEROX PARC, Palo Alto, CA, USA, 1980

- /9/ Zech, K.-A.: Extending remarks on the Eustace-Eukhopadhyay-Approach to design rule checking of integrated circuit layouts. eingereicht für EIK

Bild 2: kxR-Array zur parallelen Bewertung von k Bildzeilen. Die Eingabe der Zeilen erfolgt so, daß jede Zeile um einen Takt gegenüber der vorigen in das Feld einläuft.

ziert; nur für die letzten k-a end; Zeilen jeder Zeilengruppe wird eine Fehlerauswertung vorgenommen; die ersten a Prozessoren dienen jeweils nur der Bereitstellung der korrekten "unteren" Bewertungen für Zeile a+1.